### 平成26年度 修士論文

### High Performance Computing on Mobile Devices

電気通信大学大学院 情報理工学研究科 情報・通信工学専攻 成見研究室 学籍番号 1331098 氏名 MARTINEZ NORIEGA Edgar Josafat 指導教員 成見 哲教授 副指導教員 寺田実 准教授

平成27年1月30日

## 概要

モバイルデバイス上の高性能コンピューティング

マルチネス ノリエガ エドガー ホサファット

#### 電気通信大学

近年GPGPU (General Purpose Computing on Graphics Processors Units)が盛んになって おり、GPUを使って特定のアプリケーションを高速化することが行われている。GPUは スーパーコンピューターを構築する有効な選択肢の一つとなっており、現在のトッ プ10のスーパーコンピューター中の2台がPFlops(10<sup>15</sup>の浮動小数点演算/秒)を達成するた めにGPUが使われている。GPUはコアを沢山備えた並列処理装置であり、階層的なメ モリ構造になっている。このため、良いコストパフォーマンスが期待できる。2006年 にNVIDIAがCUDA(Compute Unified Device Architecture)をリリースして以来、GPUを簡 単にプログラムすることが出来るようになった。

一方、携帯性・低消費電力・タッチスクリーン・接続性など独特の機能を持つモバイ ル機器は、コンピュータとやり取りするための新しい潮流として興味深い進化を遂げて いる。アプリケーションプログラムから見ると、人々がどうやってデータを扱うか、ど うやってデータを可視化すべきか、などが変わってきている。モバイル機器にも何らか のGPUが内蔵されていることが多いが、ARM CPUを主流とするモバイル機器においては それ程性能を期待することは出来ない。

クラウドやグリッドコンピューティングは、サーバー側の高性能な計算能力をモバ イル機器から活用するための有望なアプローチの一つである。GPU仮想化ツールであ るDS-CUDA (Distributed-Shared CUDA)も、そのような技術の一つである。DS-CUDAは ソフトウェアレベルでGPUを仮想化するもので、クライアントマシンからローカルネット ワーク経由でリモートのGPUを透過的に使うことが出来る。ソースコードを変更しなくて も、リコンパイルするだけでGPUを搭載しないデバイスで見かけ上GPUを使ってアプリ ケーションを加速することができる。しかし、クライアントとサーバ間の通信がボトル ネックになる可能性がある。

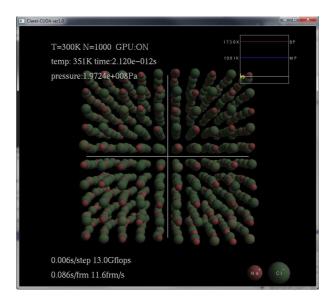

本研究では、Androidデバイス上でNaClの分子動力学シミュレーションを加速し

た。DS-CUDAを使うことでGPUを使って原子間の力及び速度の計算を高速化することが 出来た。もともとLinuxしかサポートされていなかったDS-CUDAをAndroid上で動作させ るために、NDK(ネイティブ開発キット)を用いてCコードを動作させ、OpenGL ES 1.1を 用いて描画した。クライアントマシンとしてNVIDIAのSHIELDタブレットを使用し、 サーバとしてGeForce GTX 680Mが搭載されているノートパソコンを使用した。サーバー はKnoppix 7.1 とCUDA 6.0上で動作させた。当研究ではKnoppix内にGPUやCUDA,DS-CUDAを動作させる環境を組み込んだは「Knoppix for CUDA」と呼ぶディストリビュー ションを作っており、そのDVDからブートするだけでDS-CUDAサーバーが構築できる。

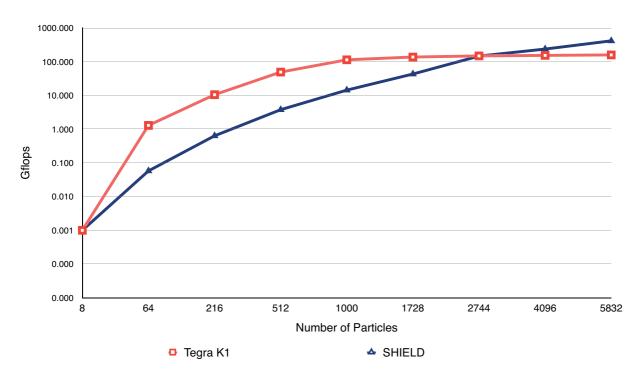

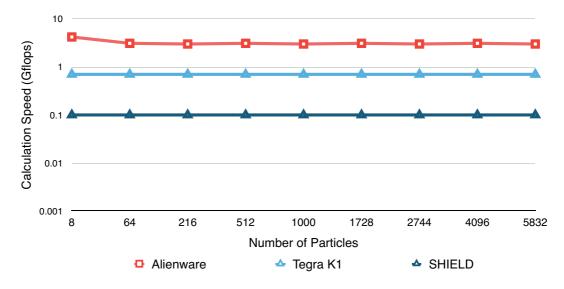

5,832原子のシミュレーションを行った場合、SHIELDタブレットのCPU上では0.073 GFLOPSの速度しか出なかったものが、本研究により5700倍高速の420 GFLOPSの計算速 度を達成した。システムのボトルネックは主にネットワークの帯域幅であるが、原子数 が多い場合(例えば5,382原子)には球を描画するルーチンがネックであることが分かっ た。原子数が多い場合は計算量が大きくなるため相対的にネットワークはボトルネックと はならない。

### ABSTRACT

#### High Performance Computing on Mobile Devices

by

MARTINEZ NORIEGA Edgar Josafat The University of Electro-Communications Professor Narumi Tetsu

GPGPU (General Purpose Computing on Graphics Processors Units) has become one of the most common ways to accelerate scientific applications and built supercomputers. At the present time, 2/10 top supercomputers are equipped with GPUs to achieve PFlops ( $10^{15}$ floating operation per second) of performance. The GPU is designed with massively programmable parallel processors, different memory hierarchy and many core chips, thus are really attractive due to its performance/cost benefit. NVIDIA is one of the pioneers to offer an easy way to program and develop for GPUs through CUDA (Compute Unified Device Architecture), released in 2006.

On the other hand, mobile devices are becoming another interesting way to interact with computers due to its specific and particular capabilities:mobility, portability, low power consumption, touch-screen, connectivity, and others. In this scenario, applications are changing the direction in which people interact and visualize data. Mobile devices are dotted with GPUs as well, however these ones cannot be easily used to achieve more performance than only using the mobile processor e.g ARM.

Cloud or grid computing is one of the promising approaches to exploit the computing power on the server side for mobile devices using high performance computing frameworks such as DS-CUDA (Distributed-Shared CUDA). DS-CUDA is a GPU virtualization tool at software level that allow us to borrow an NVIDIA GPU remotely from our local network to accelerate an app inside of a device/computer which does not contain a physical GPU. DS-CUDA enables us to use our own CUDA source code without any major modifications to accelerate the application, however communication between the client and server might become bottleneck. We implemented an NaCl MD (Molecular Dynamics) simulation with CUDA on an Android Device. On the simulator the behaviour between several ions of Na+ and Cl- at vacuum level is shown. We accelerate the computation of force, velocity and coordinate using CUDA via DS-CUDA. Other process are running on C code through NDK (Native Development Kit) and OpenGL ES 1.1 is used for rendering the visuals. We used an NVIDIA's SHIELD tablet as a client, and a laptop as a server equipped with GeForce GTX 680M running with Knoppix 7.1 linux and CUDA 6.0. The server can be built just by booting from "KNOPPIX for CUDA" DVD, which we distribute on the web. The server is connected via wired Gigabit-ethernet to our access point and the client is connected via Wifi 802.11n. We reached up to 420 Gflops in force computation on a simulation with 5,832 ions, 5,700 times faster than the 0.073 Gflops delivered from CPU implementation on SHIELD. The bottleneck in our simulation is the bandwidth delivered from our local LAN, although we tried to minimize the communication between server and client, updating every 100 MD steps. Rendering the spheres is also a bottleneck in the application, for large amount of particles (5,382 ions), however the amount of operations per second becomes larger as the number of bodies increases.

### ACKNOWLEDGEMENTS

Special thanks goes to Professor Narumi Tetsu for all its support since the beginning of this journey. For all its advices, knowledge and encourage to continue. For all opportunities he had gave me and believed in me. For all support during my permanency in Japan. Also to Professor Terada for leading this project. As well as for Dr. Oikawa and Dr. Takai for their valuable advices over DS-CUDA and molecular dynamics. I want to express gratitude as well to Dr. Rio which helps a lot in our inter ship in Saudi. To professor Dr. Yasuoka and all CREST members for giving me the chance to form part of it. For profesor Atsushi Kawai who has tough me everything of DS-CUDA and also its special support during hard times. To professor Suwako who has driven me for a lot of new opportunities and various points of view.

Special thanks to my friends Kadri and Waya, for their big support during this 3 years in Japan. To all my lab members for their support in my Japanese language, specially Shiotani Kun.

To all my family in Mexico for their unconditional support. To all my cousins for all their experiences and support. To my mother Edith and father Raul who have been the pillars of my education and support in all my professional career and life. To my brother Raul who has been an inspiration to follow and my best friend in life.

Lastly, special thanks to MengMeng Wang for her special support.

# Contents

|          | Abs  | tractI                                     | Π  |

|----------|------|--------------------------------------------|----|

|          | Ack  | nowledgements                              | V  |

|          | List | of Tables                                  | [X |

|          | List | of Figures                                 | XI |

| 1        | Intr | roduction                                  | 1  |

|          | 1.1  | Research Purpose - Objective               | 3  |

|          | 1.2  | Thesis Organization                        | 5  |

| <b>2</b> | CU   | DA                                         | 7  |

|          | 2.1  | Compute Unified Device Architecture - CUDA | 7  |

|          | 2.2  | Programming Model                          | 9  |

|          |      | 2.2.1 Kernels                              | 9  |

|          |      | 2.2.2 Thread Management                    | 11 |

|          |      | 2.2.3 Memory                               | 11 |

|          | 2.3  | CUDA for mobile architectures              | 14 |

| 3        | Mo   | bile Devices                               | 15 |

|          | 3.1  | First mobile devices an its capabilities   | 15 |

|          | 3.2  | Post PC devices                            | 17 |

|          |      | 3.2.1 Main Capabilities                    | 17 |

|          | 3.3  | Android Ecosystem                          | 18 |

|          |      | 3.3.1 Programming model                    | 18 |

|          |      | 3.3.2 OpenGL ES                            | 19 |

|          |      | 3.3.3 Native Development Kit               | 19 |

| 4        | DS-  | -CUDA                                      | 21 |

|          | 4.1  | Overview                                   | 21 |

|          | 4.2  | Package Description                        | 22 |

|          | 4.3  | Usage                                      | 23 |

|          |      | 4.3.1 Installation                         | 23 |

|          |      | 4.3.2 Configuration                        | 24 |

|          |      |                                            | 25 |

|          | 4.4  | Development Contributions for DS-CUDA      | 26 |

|          |      | 4.4.1 Enabling Android Tablets             | 27 |

|          |       | 4.4.2           | Using Native Development Kit for Android                                                                | 31 |

|----------|-------|-----------------|---------------------------------------------------------------------------------------------------------|----|

|          |       | 4.4.3           | Makefile script for DS-CUDA SDK                                                                         | 35 |

|          |       | 4.4.4           | Github repository for DS-CUDA                                                                           | 36 |

| <b>5</b> | Cla   | $_{\rm ret,Mo}$ | olecular Dynamics visualization software                                                                | 39 |

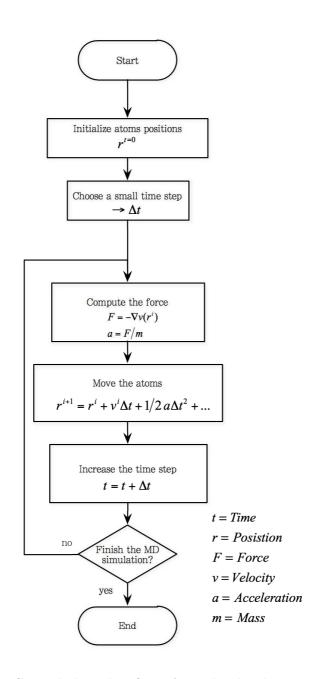

|          | 5.1   | Gener           | al Process of MD simulation                                                                             | 39 |

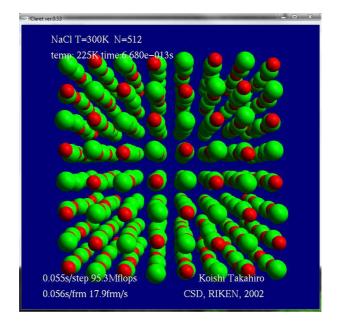

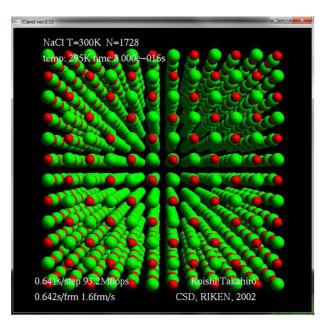

|          | 5.2   | Claret          | t overview                                                                                              | 41 |

|          | 5.3   | Techn           | ical Specifications                                                                                     | 43 |

|          |       | 5.3.1           | Force calculation                                                                                       | 44 |

|          | 5.4   | Versio          | ons                                                                                                     | 44 |

|          |       | 5.4.1           | Claret V 0.11                                                                                           | 45 |

|          |       | 5.4.2           | Claret V 0.53 $\ldots$ | 45 |

|          |       | 5.4.3           | Claret V 1.0                                                                                            | 46 |

|          | 5.5   | Andro           | pid Port                                                                                                | 47 |

|          |       | 5.5.1           | Visualization using OpenGL ES 1.1                                                                       | 48 |

|          |       | 5.5.2           | Enabling DS-CUDA for force computation                                                                  | 51 |

| 6        | Eva   | luatio          | n of Claret over different systems                                                                      | 55 |

|          | 6.1   | Syster          | m architecture                                                                                          | 55 |

|          | 6.2   | Bandy           | width performance over different mediums                                                                | 57 |

|          | 6.3   | Claret          | t performance model                                                                                     | 60 |

| 7        | Cor   | nclusio         | n                                                                                                       | 69 |

|          | 7.1   | Futur           | e Work                                                                                                  | 70 |

| R        | efere | nces            |                                                                                                         | 71 |

# LIST OF FIGURES

| 1.1        | Prototype of Mobile-HPC app 1. Galaxy simulation.                        | 4               |

|------------|--------------------------------------------------------------------------|-----------------|

| 1.2        | Prototype of Mobile-HPC app 2. Molecular Dynamics                        | 4               |

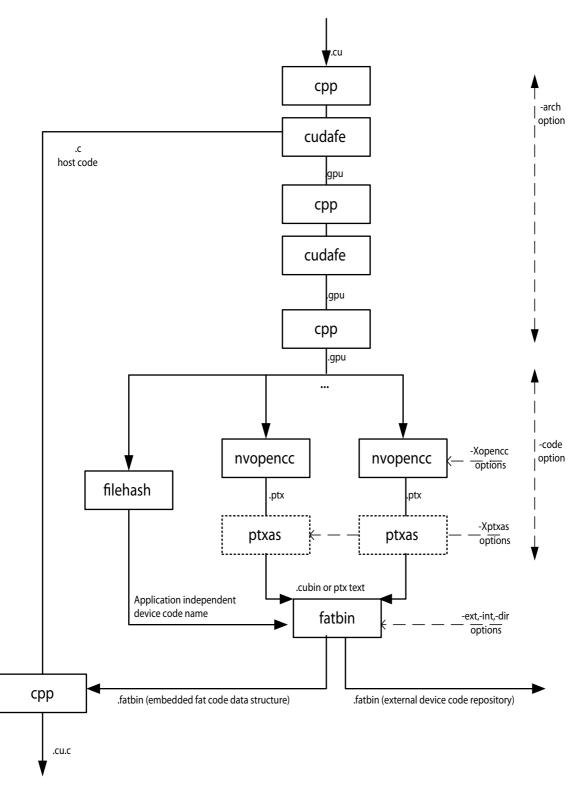

| 2.1        | Nvcc complete compilation trajectory.                                    | 10              |

| 2.1<br>2.2 | Threads organization inside of CUDA architecture.                        | 10              |

|            |                                                                          |                 |

| 2.3        | Organization of CUDA memory.                                             | 13              |

| 3.1        | Martin Cooper photographed in 2007 with his 1973 hand-held mobile phone  |                 |

|            | prototype                                                                | 16              |

| 3.2        | Palm model TX.                                                           | 16              |

| 3.3        | Various Post PC devices.                                                 | 17              |

| 3.4        | Android programming model architecture                                   | 19              |

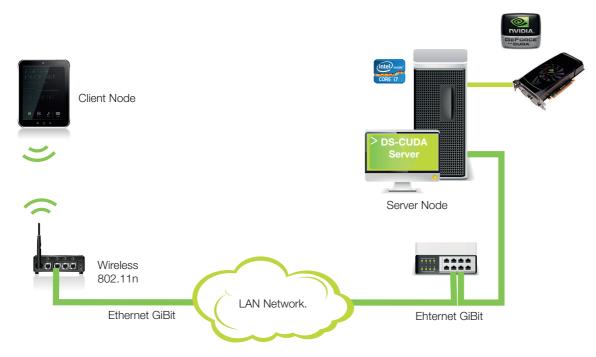

| 4.1        | Prospect of a typical DS-CUDA system.                                    | 22              |

| 4.2        | Contents of DS-CUDA package.                                             | 23              |

| 4.3        | Example of a DS-CUDA system inside of Narumi's lab.                      | $\frac{23}{24}$ |

| 4.4        | Correct execution output from a DS-CUDA server.                          | 24<br>25        |

|            | -                                                                        | $\frac{25}{26}$ |

| 4.5        | Correct execution output from a DS-CUDA client.                          |                 |

| 4.6        | System prototype to use DS-CUDA on Tablets                               | 27              |

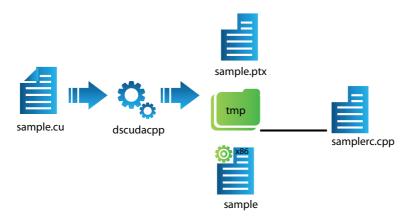

| 4.7        | Output of dscudacpp preprocessor                                         | 28              |

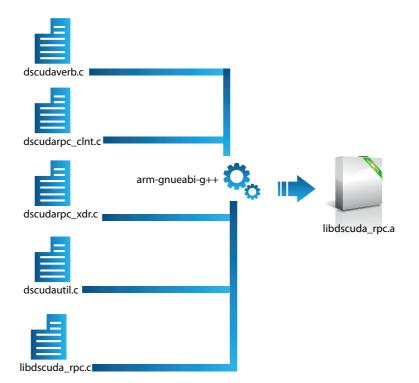

| 4.8        | Creation of client static library for ARM architecture                   | 28              |

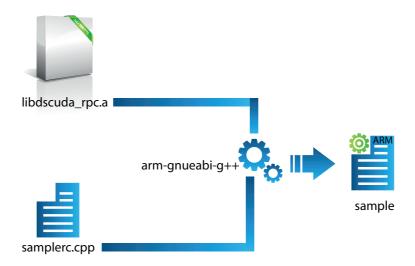

| 4.9        | Creation DS-CUDA executable for ARM architecture                         | 29              |

| 4.10       | Copy DS-CUDA executable to tablet.                                       | 29              |

| 4.11       | DS-CUDA executed on Android terminal emulator                            | 30              |

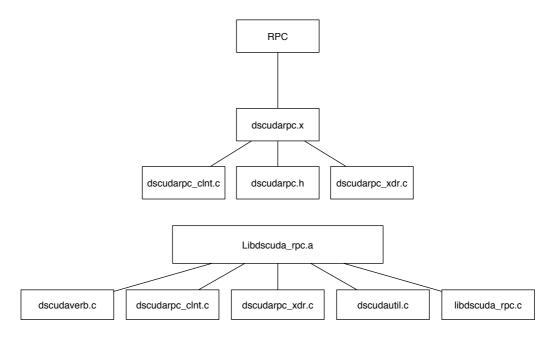

| 4.12       | Constitution of DS-CUDA client library version 1.3.2. RPC based          | 31              |

| 4.13       | Constitution of DS-CUDA client library version 1.5.2. TCP socket based   | 32              |

| 4.14       | Bandwidth sample output. Tablet performing memory transfer to the remote |                 |

|            | GPU using DS-CUDA                                                        | 34              |

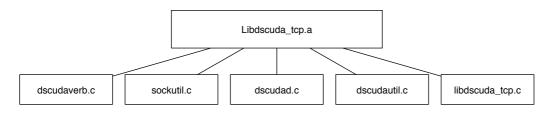

| 4.15       | Makefile script algorithm for DS-CUDA SDK                                | 36              |

| 4.16       | DS-CUDA SDK generated with our makefile script                           | 37              |

| 5.1        | General algorithm flow of a molecular dynamic simulation                 | 40              |

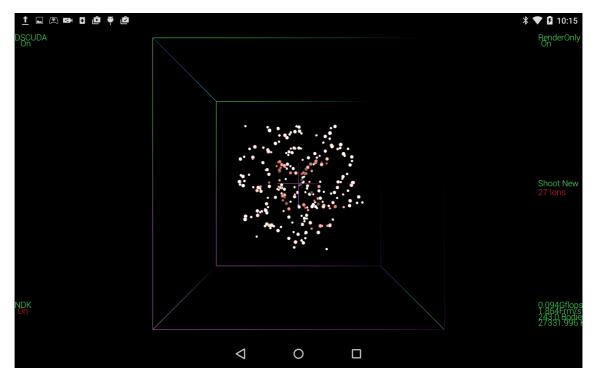

| 5.2        | Claret simulator, screen-shot.                                           | 41              |

| 5.3        | Claret simulator V 0.11                                                  | 45              |

| 5.4        | Claret simulator V 0.53                                                  | 46              |

| 0.4        |                                                                          | 40              |

| 5.5  | Claret simulator V 1.0                                         | 47 |

|------|----------------------------------------------------------------|----|

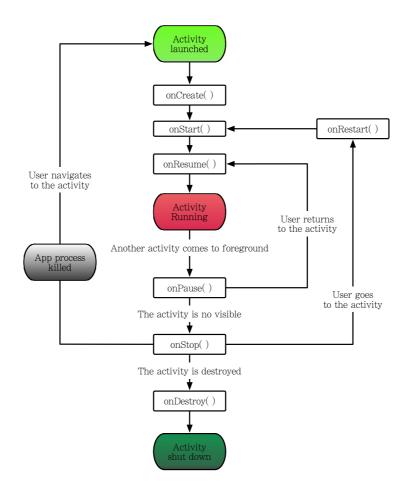

| 5.6  | Android application life cycle                                 | 49 |

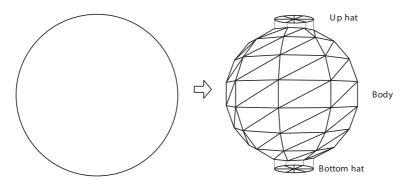

| 5.7  | Sphere structure mapped by triangle primitives                 | 50 |

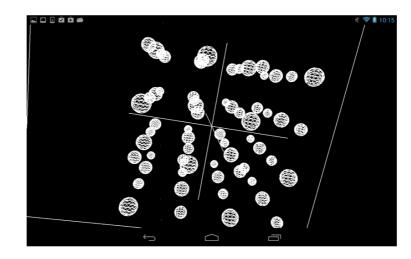

| 5.8  | First claret version on Android tablet                         | 51 |

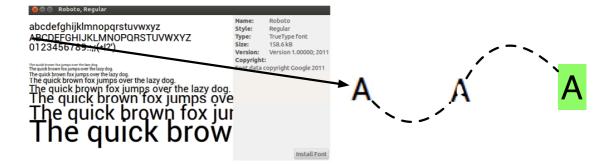

| 5.9  | Font rendering using textures and .ttf file                    | 51 |

| 5.10 | Output of claret for Android. Last version.                    | 53 |

| 6.1  | System components overview.                                    | 56 |

| 6.2  | Jetson K1 development kit.                                     | 57 |

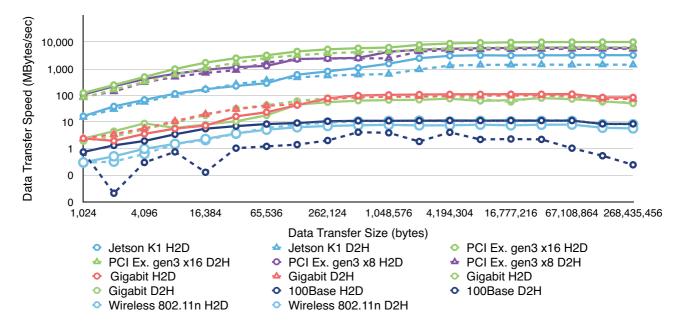

| 6.3  | Total performance of cudaMemcpy over different mediums         | 59 |

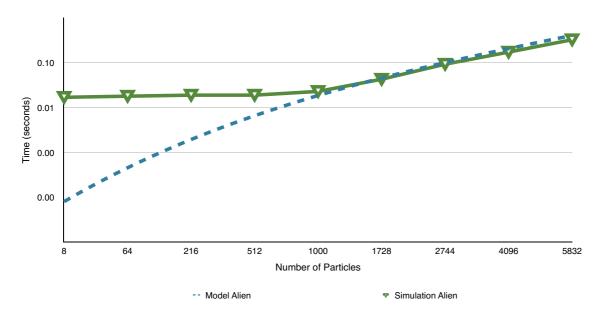

| 6.4  | Total claret performance on Alienware - Model vs Simulation    | 62 |

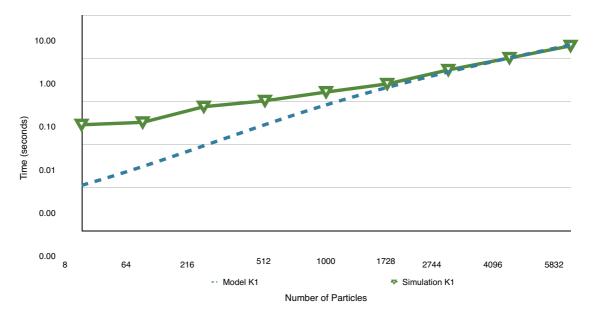

| 6.5  | Total claret performance on Jetson K1 - Model vs Simulation    | 63 |

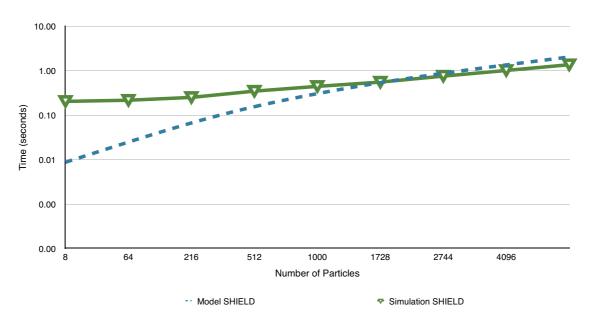

| 6.6  | Total claret performance on SHIELD - Model vs Simulation       | 63 |

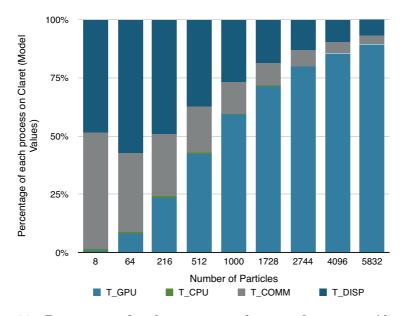

| 6.7  | Percentage of each process on claret performance - Alienware   | 64 |

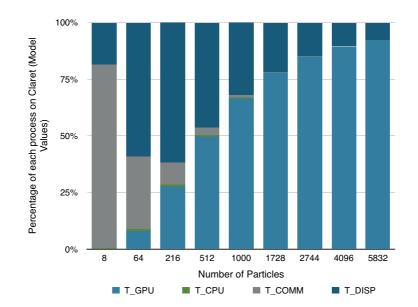

| 6.8  | Percentage of each process on claret performance - Jetson K1   | 65 |

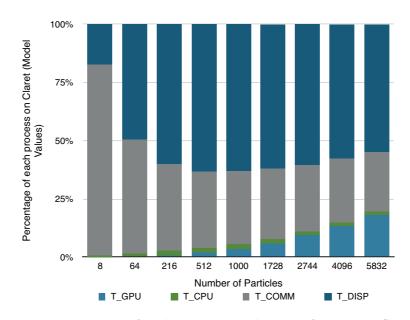

| 6.9  | Percentage of each process on claret performance - SHIELD      | 65 |

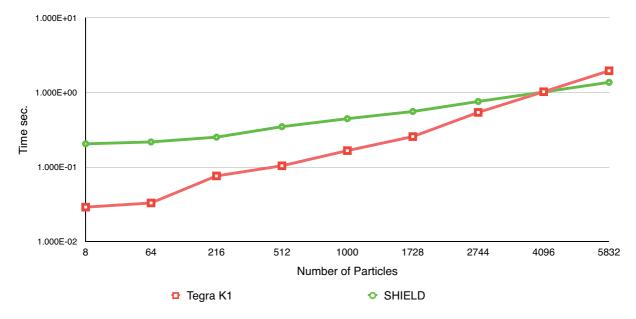

| 6.10 | Real time claret performance on Mobile Devices                 | 66 |

| 6.11 | Force computation of claret on Mobile Devices. Accelerator GPU | 66 |

| 6.12 | Force computation of claret using CPU only.                    | 67 |

# LIST OF TABLES

| 1.1 | Cost development for specialized hardware accelerators                  | 2  |

|-----|-------------------------------------------------------------------------|----|

| 2.1 | First CUDA capable GPUs and its specifications.                         | 8  |

| 2.2 | Main characteristics of CUDA memory. $W/R$ = Reading and Writing. R =   |    |

|     | Read only                                                               | 12 |

| 5.1 | List of keyboard actions inside of Claret                               | 42 |

| 5.2 | Parameters of Tosi-Fumi potential. $B = 3.15 \text{\AA}^{-1}$           | 44 |

| 5.3 | Technical specifications of Claret version for PC.                      | 48 |

| 5.4 | Differences between the usage of OpenGL / OpenGL ES over claret         | 48 |

| 6.1 | Specifications of each component of the system                          | 56 |

| 6.2 | Bandwidth performance between different mediums in MBytes. Package size |    |

|     | from 1,024 bytes to 262,124 bytes                                       | 58 |

| 6.3 | Bandwidth performance between different mediums in MBytes. Package size |    |

|     | from 524,288 bytes to 268,435,456 bytes                                 | 58 |

| 6.4 | Memory latency.                                                         | 59 |

| 6.5 | Time per particle for each process on claret on different systems       | 61 |

| 6.6 | Model and simulations results of claret performance                     | 62 |

# 1

### INTRODUCTION

High Performance Computing is a field that has been evolved through the years in the way it is applied (Software), how it is implemented (Hardware) and how we used it. In the beginning with first big computers (ancestor of the super computers) such as the Electronic Numerical Integrator Computer (ENIAC) and the Universal Automatic Computer (UNIVAC) a whole room of a building was need it to fit this only 1K Floating Operation per Second (FLOPS). The applications for his kind of machines where mainly for military purposes. One big advancement on the reduction of this big machines was the introduction of the TTL technology at the end of the 70's. Companies like Intel, ARM, Zilog, IBM and Motorola between the most famous at that time, started the development of micro processors for what will become the personal computing. Clusters and mainframes where build with these technology processors but there was a major difficulty in the programming, communication between nodes and the algorithm implementation. There has been the development as well of accelerators which are dedicated for special purposes such as molecular dynamics. These specialized hardware presents a highly parallel architecture and multi-core implementation such as the MD-GRAPE [1], Anton [2], ATOMS [3], FASTRUN [4] and C SX600 [5]. However, the development of these specialized hardware, as shown in Table 1.1, is really high considering the small scope range of their applications.

The Graphics Processor Unit (GPU) is another specialized hardware which also presents a parallel architecture design. With the advent of the graphical operating systems, the need for rendering pixels and presents into a display has been increased, and the device which encourage this task has been the GPU. Due to its primitive operations, this device is presents next characteristics:

- Low cost (Compared to other specialized hardware).

- High parallelism.

| Accelerator | Manufacture         | Estimate cost per node (USD) |

|-------------|---------------------|------------------------------|

| CX600       | ClearSpeed          | ~ \$10,00                    |

| MDGRAPE-3   | Riken               | ~ \$9,000,000                |

| ATOMS       | AT&T Bell           | ~ \$186,000 (1990)           |

| FASTRUN     | Colombia University | ~ \$17,000 (1989)            |

| GPU         | NVIDIA / ATI        | ~ \$200-800                  |

Table 1.1: Cost development for specialized hardware accelerators.

- Optimized for Floating point calculation.

- Massively programmable processors.

It was in the 70's decade when machines like Ikonas [6], the Pixel Machine [7] and Pixel Planes 5 [8] used the GPU to compute something more than pixels. Here, the General Purpose on Graphics Processing Unit (GPGPU) was born. In the same way as with the first parallel computers, managing and programing these devices for another purpose wasn't an easy task due to the buffer manipulation and other shaders which requires enough knowledge of the programming language pipeline such as OpenGL or Direct3D. Nonetheless, NVIDIA a graphic card company decided to invest in this field, creating the Compute Unified Device Architecture (CUDA) in 2006. CUDA is an architecture and programming framework that enables dramatic increases in computing performance by and easily development on GPUs. Since then, CUDA has successfully accelerated applications in many fields:

- Bio-informatics.

- Computational chemistry.

- Computational fluid dynamics.

- Computational structural mechanics.

- Data science.

- Defence.

- Computational finance.

- Imaging and Computer vision.

- Weather and climate.

- Medical imaging.

Also, some of the top of super computers, in the list of TOP500 [21] are equipped with GPUs as accelerators. In order to handle this tumultuous conglomerate of GPUs in cloud

environment some HPC frameworks has been developed such as Distributed-Shared CUDA. This framework helps to solve the major difficulties in programming multi-node heterogeneous computers virtualizing GPUs on a distributed network as if they where attached to a single node. In this sense, using a remote GPU from another device which is not equipped with one accelerator of this kind is a feasible capability of DS-CUDA.

On another scenario, mobile devices are becoming primary devices for various of our main activities such as reading email, taking pictures, playing games, using social networks and also creating our own content. Since the appearance of the "smart-phone" and tablet devices, the effort to integrate many sensors into a mobile device has lead new kind of applications and new services development. New paths to interact with data and also to represent this information to the user. Efforts to create new contents has lead a numerous variety of research topics such as visualization data, virtual reality, health based applications, between others [9] [10] [11] [12] & [13]. However, due to its mobile nature, these devices are equipped with low computation power processors such as ARM and not yet programmable GPUs. Undoubtedly, next generation of mobile device applications will will require a lot of computational power.

We proposed to merge the High Performance Computing applications with the mobile device in this research. Through DS-CUDA framework, utilize remotely CUDA capable GPU on the tablet to run an N-body simulation. An study about performance will be presented as well.

#### 1.1 Research Purpose - Objective

The main purpose of this research is to approach high performance computing applications for mobile devices. These touching screen devices hold a new way to dive into the information presented to the user. First applications prototyped by the author were galaxy simulation or molecular dynamics, Figures 1.1 & 1.2 respectively, on Tablet device. However, to reach this goal an accelerator is needed due to the low power precessing of the mobile devices. Utilizing DS-CUDA framework seems to be a feasible solution since its open source nature and the ability to use remotely a GPU from our local network.

Thus, 3 main objectives are summarized in this work:

#### First

DS-CUDA compatible with Android. In order to use remotely a GPU from our local network inside of Android tablet device we need to be able to run client libraries and generate proper DS-CUDA stubs for Android. Two approaches are presented: Using a terminal emulator and through the Java Native Development kit.

#### Second

Create an HPC application for Android. To test the performance of DS-CUDA a

Figure 1.1: Prototype of Mobile-HPC app 1. Galaxy simulation.

Figure 1.2: Prototype of Mobile-HPC app 2. Molecular Dynamics.

molecular dynamics simulation is implemented using OpenGL ES.

#### Third

Analyse the performance of the application. Modelling all the main process and communication through the simulation and identifying the bottlenecks.

#### 1.2 Thesis Organization

The present work is divided into 7 Chapters. Chapter 1 introduces all the background about the General Purpose computing using GPUs, as well as the importance of the mobile devices and its unique characteristics. Chapter 2 is about CUDA, its programming model and capabilities. Also some introduction for mobile architectures is mentioned. Chapter 3 talks about the mobile devices and its evolution, the capabilities and applications. A description of Android operating system is also included. In Chapter 4 we go through DS-CUDA framework, its overview and usage. Also, here we mentioned a contribution that we made as consequence of this research. Chapter 5 is about "claret" molecular dynamics simulation software, its main capabilities and versions. The description of the port for Android is detailed here. The evaluation of the performance of claret is remarked in Chapter 6, as well as the system architecture prepared for the test evaluation. Last Chapter 7 some remarks and conclusion are listed.

### CUDA

The graphics cards are designed to render high-quality 3D textures in real time. Due to the large competitive market in this range of devices, the Graphic Processing Unit (GPU) has become a powerful hardware for computing comparatively for low Cost. Interestingly, this hardware become able to compute any kind of data rather than only pixels inside of shaders. This new paradigm has its origins based on the General Purpose Computing on Graphics Processing Units (GPGPU), particularly known for their great programming difficulty due to the high level of knowledge in the graphics pipeline.

In recent years, scientist and developers have started using GPU as an accelerator for their algorithms where they can get benefit of thousands of threads of this device.

#### 2.1 Compute Unified Device Architecture - CUDA

CUDA is a computing architecture and framework developed by NVIDIA, a graphic card company, with the main purpose of facilitate the parallel programming of GPUs. CUDA allow developers to get immerse into the great power that the GPU brings with its many cores and memory hierarchy. Before, graphics cards were only conceived in the high end multimedia, media design and games sector, but nowadays CUDA allows GPU to work in another kind of fields:

- Science

- Engineering

- Economy

High level of knowledge of the graphics pipeline<sup>1</sup> is not needed, and only the knowledge of C language is required.

$<sup>^{1}</sup>$ Is defined as the process or consecutive subroutines that are required to deploy graphics generated by an output device.

| Model                                                                                    | Computing<br>Capability | Multiprocessors | CUDA cores |

|------------------------------------------------------------------------------------------|-------------------------|-----------------|------------|

| GeForce GTX 560 Ti                                                                       | 2.1                     | 8               | 384        |

| GeForce GTX 460                                                                          | 2.1                     | 7               | 336        |

| GeForce GTX 470M                                                                         | 2.1                     | 6               | 288        |

| GeForce GTS 450, GTX<br>460M                                                             | 2.1                     | 4               | 192        |

| GeForce GT 445M                                                                          | 2.1                     | 3               | 144        |

| GeForce GT 430, GT<br>440, GT 435M, GT<br>425M, GT 420M                                  | 2.1                     | 2               | 96         |

| GeForce GT 520, GT 415M                                                                  | 2.1                     | 1               | 48         |

| GeForce GTX 580                                                                          | 2.0                     | 16              | 512        |

| GeForce GTX 570,<br>GTX 480                                                              | 2.0                     | 15              | 480        |

| GeForce GT 470                                                                           | 2.0                     | 14              | 448        |

| GeForce GTX 465,<br>GTX 480M                                                             | 2.0                     | 11              | 352        |

| GeForce 295                                                                              | 1.3                     | 2x30            | 2x240      |

| GeForce GTX 285,<br>GTX 280, GTX 275                                                     | 1.3                     | 30              | 240        |

| GeForce GTX 260                                                                          | 1.3                     | 24              | 192        |

| GeForce 9800 GX2                                                                         | 1.1                     | 2x16            | 2x128      |

| GeForce GTS 250, GTS<br>150, 9800 GTX, 9800<br>GTX+, 8800 GTS 512,<br>GTX 285M, GTX 280M | 1.1                     | 16              | 128        |

| GeForce 8800 Ultra,<br>8800 GTX                                                          | 1.0                     | 16              | 128        |

| GeForce 9800 GT, 8800<br>GT                                                              | 1.1                     | 14              | 112        |

Chapter 2 CUDA

Table 2.1: First CUDA capable GPUs and its specifications.

It wasn't until five years later of the presentation of GeForce<sup>2</sup> 3 that the general purpose computing was ready for its first steps. In November of 2006, NVIDIA introduced to the world the first CUDA capable GPU GeForce 8800 GTX. This DirectX 10 capable GPU bring the first speed up on science and start the revolution of GPGPU. Since then, NVIDIA continues to develop and release new CUDA capable graphic cards. Table 2.1 shows some of the first CUDA capable devices.

Since NVIDIA wanted to create a whole new family of graphics processing unit for general purpose computing the Arithmetic Logic Unit (ALU) were designed under the standard IEEE 754-1985 [18] for single floating point precision, as well as including many functions not oriented to graphics rendering. Also they implemented a whole new memory hierarchy inside

<sup>&</sup>lt;sup>2</sup>One of the most famous NVIDIA's GPU branch, dedicated to gamers and high end multimedia PC.

of the device composed up to 5 levels. All of this and other great capabilities are included in CUDA allowing GPU's to achieve general purpose computing and also graphics rendering.

#### 2.2 Programming Model

A structure of a CUDA program is grouped in one or more phases that are executed in the *host* (CPU) or inside of the *device* (GPU). The parts inside of the code which shows a lot of parallelism are executed inside of the device. In the other hand, the serial parts are running in the host side. Thus, a CUDA program is a combination of code execution inside of host and device. NVIDIA provides an special based C compiler called *nvcc* which separates and process the different code for each device, as the Figure<sup>3</sup> 2.1 shows. The code that belongs to the host is ANSI C standard, process by normal C language compilers and runs in an "commercial" CPU. The code executed in the device is processed in some different ANSI C standard that extend key-words for parallel functions called *kernels* and its associated data structures.

#### 2.2.1 Kernels

The called *kernels* are subroutines executed inside of the GPU which in turn call a massive number of *threads*. Each GPU is composed for many Multiprocessors (MP) which also contains tons of threads. Depending of the compute capability, the developer may launch up to 1024 threads per MP or more. In this way, one thread does not process the same information at the same time since each one have a different "Index". This special identifier tells the thread what to do with different data and accessing different memory region. Next, we provided a very easy sample of a kernel.

```

1

```

```

\mathbf{2}

// Strucutre of a Kernel

__global__ void MiKernel(float* x, float* v, float cons)

3

{

4

int i = threadIdx.x;

5

x[i] = x[i] + v [i] * cons;

6

7

}

8

. . . . . .

9

. . . . . .

10

. . . . . .

int main()

11

12

{

```

<sup>&</sup>lt;sup>3</sup>Image courtesy of http://developer.nvidia.com//nvidia-gpu-computing-documentation//

Figure 2.1: Nvcc complete compilation trajectory.

As we can see in the kernel sample, an especial identifier of it is the reserve word **\_\_global\_\_** in which the developer can specify the number of threads to be launched in side of the GPU. This is done through the identifier <<<....>>>. The special index for each thread is reachable by one *built-in* variable called **threadIdx**. This patern operates in the paradigm *Single Instruction, Multiple Data* (SIMD) which is used typically on the GPU, contrary to the CPU which uses *Single Instruction, Single Data* (SISD). Also, the kernel allows sentences like "if-then-else". NVIDIA has developed the concept of *Single Instruction, Multiple Thread* (SIMT). One example of this new concept is executing code depending if the index of a thread is odd or even. However, to get the best inside of a GPU we have to take care of details such as the called *warp*. This means that if each MP contains 8 processors only 32 threads will be executed at the same time, then the developer should be able to consider conflict of memory between the access of the indexes.

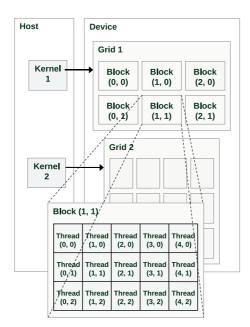

#### 2.2.2 Thread Management

Conveniently, the variable **threadIdx** is a 3 component vector that can identify threads by an Unidimensional (1D), Bi-dimensional (2D) or Tree-dimensional (3D) arrangement.

• threadIdx.x, threadIdx.y y threadIdx.z

This bunch of threads get grouped into blocks, which can be collapsed by 1D, 2D and 3D index variable **blockIdx**.

• blockIdx.x , blockIdx.y y blockIdx.z

This naturally offers a way to invoke elements in cross connection such as vector, matrix or volume. Blocks are organized into a grid, as is shown in Figure 2.2.

There is a limit of threads that the coder can call per block. In actual GPUs the limit is over 1024 threads, this is due to special memory segment shared for all threads inside of the same MP and the architecture of the GPU itself. Nevertheless, a kernel is able to execute a multiple amount of blocks per time. Thus, the total number of threads is equal to the number of threads per block times the number of blocks.

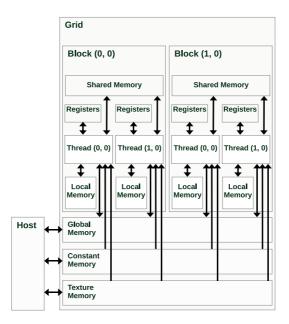

#### 2.2.3 Memory

NVIDIA's GPUs are equipped with 5 different memory, each of one with different characteristics and functionality. Its crucial its understanding in the path of seraching the best

Figure 2.2: Threads organization inside of CUDA architecture.

| Memory | Global                     | Constant    | Texture                    | Shared    | Local                      |

|--------|----------------------------|-------------|----------------------------|-----------|----------------------------|

| Access | W/R                        | R           | R                          | W/R       | W/R                        |

| Size   | More than $100 \text{ MB}$ | 64  KB      | More than $100 \text{ MB}$ | 16  KB    | More than $100 \text{ MB}$ |

| Scope  | Application                | Application | Application                | Per Block | Per Thread                 |

Table 2.2: Main characteristics of CUDA memory. W/R = Reading and Writing. R = Read only.

performance on the GPGPU. Table 2.2 refers to main characteristics of this memory spaces. Next we will a brief description and usage of this 5 different memory spaces.

#### Global Memory

This is the main memory zone that a kernel is able to write and read data. Dynamic memory allocation on the fly is not allowed, it must be allocated before the application starts. This memory is variable according to the GPU model and nowadays goes beyond the 1GB. During the kernel call, this memory space is persistent.

#### Constant Memory

The constant memory is very small, reaching only 16KB and "read" only. This space is persistent along the kernel calls. The host can load any kind of data inside of this space of memory. Read only refers that inside of a kernel this space can not be modified by the device.

#### Texture Memory

This memory space is quick and read only. Specialized to load mapping and modelling elements in 2D and 3D. CUDA offers to the ability to communicate with graphics pipelines

Figure 2.3: Organization of CUDA memory.

such as OpenGL and Direct X in order to save time reaching objects in space memory, thereby, the rendering time is faster.

#### Shared Memory

The shared memory is small space, about 16KB which does not resides inside of the main memory and it is not persistent along the kernel's call. The host can not load any data, however, when the host call the kernel, this can specify up to 16KB read and write zone for all the threads within a block. In this way, all the threads inside of a block share this memory space. After the last execution of the last thread, this space is unallocated. Using this memory space is faster than the global memory for the same threads within a block.

#### Local Memory

Local memory has similar functions to global memory, only the life time and the variable scope are limited to one single thread. The main reason is as follows: If every MP can run up to 1024 threads concurrently and only 16384<sup>4</sup> register, each thread can only use 16 of them with full load. If more different variables are need at the same time, these will be allocated in the local memory. Unfortunately, this choice is left for the compiler in order to save registers.

As the Figure 2.3 shows, CUDA architecture has various different types of memory, which can be not so easy so manage but that the developer can used according to his needs. This may impact directly to the performance of the final CUDA application.

<sup>&</sup>lt;sup>4</sup>The exact number of register of GPU may vary with a different model version.

#### 2.3 CUDA for mobile architectures

With the increase usage of smart phones and tablets, new processors architectures were developed such as ARM architecture, in order to follow the special computing and power demand that these new devices requires for daily task. NVIDIA's company, as graphics accelerator hardware pioneer enter to this market with the introduction of a new branch of mobile processors called Tegra. This system on chip (SoC) is aimed for mobile devices such as smartphones, digital cameras, personal digital assistants and internet mobile devices. Trough many iterations of this new SoC, Tegra APX, Tegra 2, 3 and 4 this new branch of NVIDIA's processor took a place in mobile market. However, all of these chips are not CUDA capable.

It was on April 2014 when NVIDIA finally released one mobile chip capable of CUDA architecture, Tegra K1. This new ARM cortex general purpose 32 bit processor includes a general-purpose GPU. Also is able to run OpenGL ES 3.1, CUDA 6.5 and OpenGL 4.4. The company claims that it outperforms both Xbox 360 and PS3 whilst consuming significantly less power.

Some of the motivations to use this new chip are solutions for compute-intensive embedded projects like autonomous robotic systems, advance driver assistance systems, mobile medical imaging and intelligent video analytics.

### MOBILE DEVICES

The human has the basic need of communication, and since the technology appears, we haven't stopped searching for better, new, crazy and innovative ways of transmit information between each other. Commodity is also an strong point when we think about technology development, thus mobility. Maybe one of the most important events on the development of the human communication history is the invention of the telephone which allow the globe to become a vast network of electricity-based speaking people. With the arrived of transistor and micro electronic components, the compute devices started to become smaller and smaller, and with the integration of the radio wave technology, the first clues of mobile devices start to appear. Changing the way we communicate, where and how, the mobile phone is maybe one of the most important devices nowadays, which changes and creates industries and businesses. Not only the usage of mobile phones but also the Personal Digital Assistant (PDA), tablets, music players, watches, video game portable devices, and GPS are now part of our daily life, and sometimes essentials.

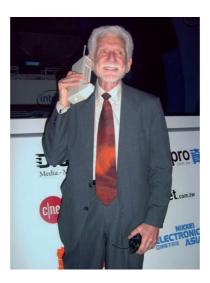

#### 3.1 First mobile devices an its capabilities

The radio telephony used in the second world war is the predecessor of the existing mobile phones. At the same time, telephones on auto-mobiles were possible however not so famous and common to use. AT&T company was the first in commercialized a Mobile Service Telephone in 1949. In 1973 Martin Cooper from Motorola introduce the first mobile called "the brick" [28] as is shown<sup>1</sup> in Figure 3.1. It was capable of 60 minutes of talking however taking 10 hours to get full charge.

Another mobile device, which impact over the society and the way we live was the Sony's Walkman. In 1979 the first portable cassette tape was on sale for \$150 dollars [29]. Power consumption was low requiring only either one AA battery or one gumstick-type rechargeable.

<sup>&</sup>lt;sup>1</sup>Images courtesy of "2007Computex e21-MartinCooper" by 2007Computex-e21Forum-MartinCooper.jpg

Figure 3.2: Palm model TX.

This small device, change a way in which used to enjyousic in a travel, on the public transport and also when we do fitness activities.

The introduction of PDAs or personal data assistant were the first steps of what we know common today as a tablet or handheld PC. the calle dPDA has an electronic visual display, including a web browser, capable of playing audio as a portable media player. Most of PDAs have access to internet, intra-nets or extra-nets via Wi-Fi and most importantly utilizes touch technology. One example is the Palm TX which is shown<sup>2</sup> in Figure 3.3.

Perhaps another big mobile which made a huge impact in the way of its application is the Nintendo GameBoy. Released in Japan in 1989, this is one of the first mobile consoles to has a tremendous success. Holding the purpose of playing video games only, this 15-30 hours portable game console was powered by 4 AA batteries. It was included in the system a CPU custom 8 bit processor at 4.19 MHz.

As we can denote from the devices mentioned before, they were the first on its category, moving forward the technology and evolving the way of communication. Strongly, we can observe that the functionality was limited to one main function, the battery life was mention

<sup>&</sup>lt;sup>2</sup>Images courtesy of Palm T—X Photographer: Stefano Palazzo Used Camera: Kodak Z740

Figure 3.3: Various Post PC devices.

to have a period of hours and the interactivity with the user was tied.

#### 3.2 Post PC devices

During the end of the 90's and the first half of new millennium, the cellular phone was consider the gadget of the moment. Accompanied with the first PDAs and the popularity of Internet, this mobile devices were doted all ready with the first mobile OS, such as Palm OS, Black Berry OS, Windows CE/Pcoket PC or Simbian. These small apparatus, as the ones shown<sup>3</sup> in the Figure 3.3, were developed to deliver more than one main function to the user, making them more intuitively and dynamic, thus more complex in design and powerful. But it wasn't until 2007 when Apple introduce the iPhone that the real-smart phone, one of the most important Post PC devices, came along to the scenario to define a new way to interact with mobile computers. Since then, multiple devices such as Tablets, E-Readers, smart-watches and others, make usage of new technologies to increase the capabilities, functionality, computation performance, interactivity and services which provides a unique experience to the users.

#### 3.2.1 Main Capabilities

Possibly, the greatest impact of the Post PC devices over the first mobile devices are the bunch of capabilities inside of them. In the beginning, mobility was only focused on one main task due to the technology frontier and scarce resources. However, nowadays the experience is much more complete within a tablet or smart phone. Some of these new features are:

- Mobility.

- Connectivity.

<sup>&</sup>lt;sup>3</sup>Images Courtesy of Courtesy of www.isanweb.es

- Limited Memory.

- Portability.

- Huge Ecosystem.

- Low power consumption.

- Touch screen capabilities

- Low processing (ARM processors)

With these various capabilities, the applications for a mobile devices are more wide rich in experience and contents. The search for crating new contents has lead a numerous variety of research topics such as virtual reality, visualization data, health based applications, games and others [9] [10] [11] [12] & [13]. As well as this dissertation will approach the high performance computing on mobile devices through remote GPGPU.

#### 3.3 Android Ecosystem

Although, recently there are more than one operating system for mobile devices such as iOS for apple products, Windows mobile, WebOS and Ubuntu touch, the author decided to use Android due to its widely adoption through the mobile device community, Linux based architecture, more compatibility through wide range of devices and its ease of application implementation. Android is was developed by Android Inc. which was absorbed by Google in 2005. Since then Android has become one the most emblematic products of this company. Android since its first appearance has many iterations versions which are named with "desserts", such as 1.6 Donut, 2.0 Eclair, 2.2 Froyo, 2.3 Gingerbread, 3.0 Honeycomb, 4.0 Ice cream sandwich, 4.1 Jelly bean, 4.4 Kitkat and finally the most recent 5.0 Lollipop.

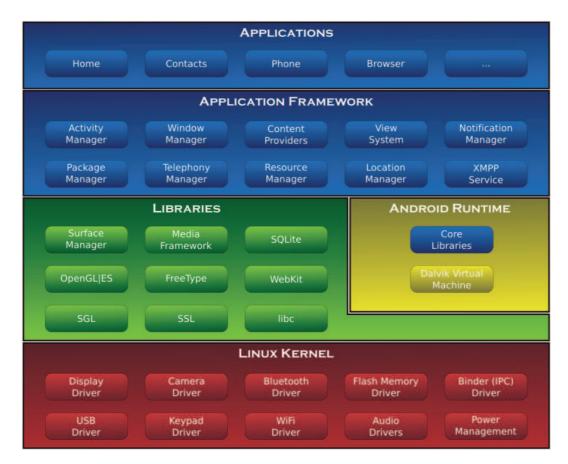

#### 3.3.1 Programming model

Android has a Linux kernel on its core, and on the top of this there are the middleware, libraries and APIs most based on C language. Also, this mobile OS contain an application framework which includes Java-Compatible bytecode. The Dalvik virtual machine is in charge of generate dex-code which is translated directly from Java bytecode. This virtual machine is optimized to use few memory which is one of the "commons" inside of mobile devices. It is designed to execute various instances. In the Figure 3.4 a general view of the programming model<sup>4</sup> is displayed.

<sup>&</sup>lt;sup>4</sup>Image courtesy of "Android-System-Architecture" by Smieh - Anatomy Physiology of an Android.

Figure 3.4: Android programming model architecture.

#### 3.3.2 OpenGL ES

OpenGL is the one the most widely known computer graphics rendering plication programming interface developed by Krhonos Group. OpenGL ES for embedded systems supports the generation of 2D and 3D graphics for smart-phones, tablets, video-game consoles and PDAs. Ti has been released various major versions such as 1.0, 1.1, 2.0 and 3.0. The similarities between the normal OpenGL API are perceptible but not identical. One of the major disadvantages for porting between these two API is that GLUT <sup>5</sup> is not included. Also OpenGL ES comes with its own shading language. Android supports OpenGL ES since the Android 1.6 version on its different major versions.

#### 3.3.3 Native Development Kit

The called NDK toolkit allows running C and C++ code inside of Android device. There are 2 good reasons why is practical to use C instead of Java language. First, the execution of C code is done natively inside of the ARM processor, intended for such applications with CPU-intensive workload such as game engines, signal processing, physics simulation and so on. Second, to use libraries which are already exist in C language code and also the usage of

<sup>&</sup>lt;sup>5</sup>OpenGL Utility Toolkit facilitate the window managing, keyboard and mouse input functions and others.

third party code. NDK set of tool-chains that can generate native ARM binaries on Linux, OS X and windows platforms. It also provides a set of system headers for stable APIs:

- libc.

- limm.

- JNI interfaces.

- libz for compression.

- liblog for Android logging.

- OpenGL ES 1.1 and 2.0.

- libjnigraphics.

- Minimal set of C++.

- OpenSL ES for native audio.

- APIS for Android native applications.

Basically NDK uses a set of ARM compilers to create static and shared libraries which are loaded by the Dalvik virtual machine. This libraries can be created by specifying correctly the *Android.mk* and *Application.mk* files. Under the folder called "jni" inside of a Android project, these two files are similar to "make" based type archives. Inside of them we can specify paths, compiler flags, directives, libraries and other C like options. Finally, a dynamic library is created which is loaded in Java code through *System.Load()* function. NDK also provides a set of sample programs (SDK) which describes how to create a shared library and included inside of your Java Code.

# 4

# DS-CUDA

Super computers and clusters inside of the High Performance Computing (HPC) field are nowadays equipped with several hundreds of thousand cores. Due to this large topology of CPU connections, communication among the cores tends to be the bottle neck rather than the computation itself. Moreover, as we explained in chapter 2, with the arising of GPGPU and its good welcoming from CUDA's hand, more and more scientific community integrated this devices to its HPC cluster as accelerators. Some of the top machines in the TOP500 [21] list are also equipped with GPUs. However, a limiting point is the ability to allocate a few GPUs inside of each PC. Therefore, the scenario to implement an algorithm inside of this massively parallel system may be that the developer applies at least three common HPC frameworks: MPI,OpenMP and CUDA. Even a complicated program using all three frameworks may fail to take full advantage of the system performance. In addition, in some cases we have a machine which is not equipped with a GPU, and using them from our local network may benefit educational and demonstrative purposes.

To solve this kind of difficulties, HPC frameworks have arisen such as Distributed-Shared CUDA (DS-CUDA).

#### 4.1 Overview

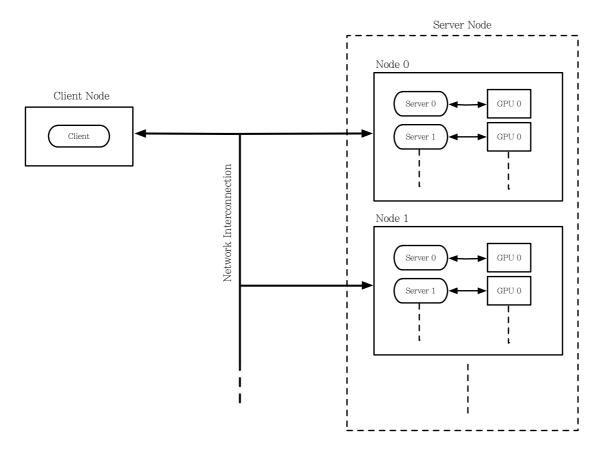

DS-CUDA is a middleware that allows to manage NVIDIA's GPUs on a distributed network. A single client node and various server nodes compose one DS-CUDA system, as is shown in Figure 4.1. The server nodes have one or more CUDA capable GPUs that are handled by server processes. An application on the client side can use these parallel devices to process data without having a physical GPU. The program sees all GPUs contained into a cluster as if they were actually attached to the client node. Therefore, DS-CUDA is a kind of GPU-virtualization tool at source code level.

When the client calls native CUDA API, the DS-CUDA preprocessor handles the correct

Figure 4.1: Prospect of a typical DS-CUDA system.

wrapper function, which communicates with the server nodes through an InfiniBand (IB-Verb) or TCP socket. The wrapper function sends the proper arguments and data to the server nodes, each of which process this data calling the actual native CUDA API. A detailed description of its implementation is in another paper [22] and also application [23].

#### 4.2 Package Description

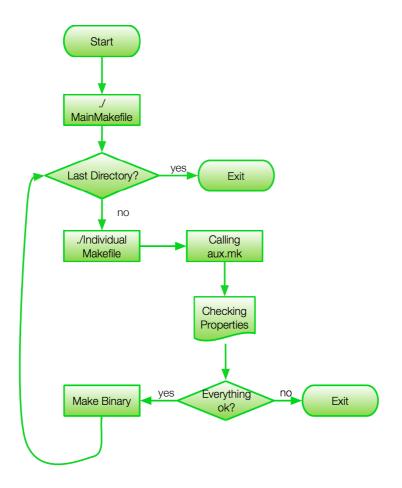

DS-CUDA is presented as an Open Source package that can be obtained from http://narumi.cs. uec.ac.jp/dscuda/ as a .tar package. Contents of this package are listed in Figure 4.2. As the image shows, the contents are all binaries including the *dscudacpp* which is a preprocessor who handles the kernels calls inside of the client side. A brief documentation is also included, such as a quick start.However, more detailed explanation is a viable in Japanese at the moment. Some examples are also part of DS-CUDA package, including bandwidth program which measure performance of *cudaMemcpy* function<sup>1</sup>. Claret sample which shows a molecular dynamics simulation between Na Cl particles. Direct sample which copy memory between GPU's using peer to peer function. Matrix multiplication program and the last one which shows a basic computation of adding two numbers such as a + b = c. Nevertheless,

<sup>&</sup>lt;sup>1</sup>This function copy memory between the host (CPU) and the device (GPU).

1. Default (ssh)

```

edgar@Edgar-PC:/usr/local/DSCUDA/DSCUDAlegacy/DSCUDA/dscudapkg1.3.2$ tree -d

```

```

I-- bin

I-- doc

I-- include

I-- lib

I-- sample

I-- bandwidth

-- dscudatmp

1

I-- claret

I-- dscudatmp

-- table

I-- direct

matrixMul

1-

I-- dscudatmp

-- tmp

vecadd

I

-- dscudatmp

I

I-- script

`-- src

```

Figure 4.2: Contents of DS-CUDA package.

DS-CUDA framework continues in development and it's keeping adding more contents and capabilities which may be different as the ones mentioned here.

### 4.3 Usage

As we were mentioned before, DS-CUDA was born as a high performance computing framework for NVIDIA's GPUs. This means, that clusters and supercomputers were the main target of this new technology. One more real example is the one shown in Figure 4.3. In this system configuration we can appreciate one client machine without any physical GPU. Also, various server nodes with up to 2 GPU per node.

DS-CUDA runs mainly over Linux based operating systems. Main developers and testers have used distributions such as Knoppix 7.2, Ubuntu 12.04, Ubuntu 14.04 and Fedora 12 to test the package. DS-CUDA works properly with x86 32-bit and 64 bit architectures. One important thing to consider is the communication medium between client and server, such as Inifni-Band verbs or TCP socket. For the first one, you may need the proper libraries and also the device and infrastructure to interconnect your machines. To use TCP socket, Ethernet cable or Wi-fi is used, which is the most common option to test DS-CUDA.

### 4.3.1 Installation

In order to run DS-CUDA, make sure that your machine includes the following packages and tools:

• CUDA Toolkit & SDK (Tested with 4.1 5.5 and 6.0)

Figure 4.3: Example of a DS-CUDA system inside of Narumi's lab.

- GNU C++ compiler (Tested with version 4.5 and above)

- Ruby (Tested with version 1.8 and above)

- OFED (Tested with version 1.5) for Infini-Band support.

Once the package is downloaded and extracted, go directly to **\$dscudapath/src**. Inside of this directory all the source code is included and through the *make* command you can generate binaries and libraries for client and server, such as :

- $dscudapath/bin/dscudasvr \rightarrow DS-CUDA$  server executable.

- $dscudapath/lib/libdscuda_rpc.a \rightarrow DS-CUDA$  client library (TCP socket).

- $dscudapath/lib/libdscuda_ibv.a \rightarrow DS-CUDA$  client library (IB verb).

- $dscudapath/lib/libcudart.so \rightarrow Dummy CUDA runtime library.$

### 4.3.2 Configuration

The program running inside of a DS-CUDA client sees virtual devices that are real devices allocated in the server. The mapping of the real virtual devices is given by an environment variable<sup>2</sup> DSCUDA\_SERVER. DS-CUDA framework manages and configures through environmental variables. The ones of primary usage are listed bellow:

• DSCUDA\_PATH : Indicates the full path of the package location

$<sup>^{2}</sup>$ Environmental variables provide a way to influence software behaviour on Linux system. They are widely used for customization and configuration.

```

dscudasvr[0] : WarnLevel: 2

dscudasvr[0] : method of remote procedure call: SOCK

dscudasvr[0] : TCP port : 65433 (base + 0)

dscudasvr[0] : ndevice : 1

dscudasvr[0] : real device : 0

dscudasvr[0] : virtual device : 0

dscudasvr[0] : listening on port 65433.

```

Figure 4.4: Correct execution output from a DS-CUDA server.

- DSCUDA\_WARNLEVEL : Configures the warning level. 2 is the default value, but can be increased to 5 for debugging purposes.

- DSCUDA\_REMOTECALL : Indicates which kind of protocol is used between client and server.

- DSCUDA\_USEDAEMON :Selects the option to run a daemon which stay listening for client request

- DSCUDA\_SERVER : Configures the server host-name or "ip" address.

A complete list of DS-CUDA environmental variables refer to Japanese documentation.

### 4.3.3 Sample Test

In this section we describe a real example of DS-CUDA system test as the one depicted on Figure 4.3, using the *vecadd* sample listed in the samples of the package.

### Server Side

Once inside of the main path **\$dscudapath/src**, we can create the binary for the server. In this scenario using socket protocol connection we compile *dscudasvr*. Once generated, we need to set some minimal environmental variables such as: DSCUDA\_WARNLEVEL = 2 and DSCUDA\_REMOTECALL = tcp. Done the mentioned above, we can lunch the program, obtaining an output similar to the Figure 4.4.

On the output of the DS-CUDA server we can observe some useful details: warning level execution, the communication protocol between server and client, number of real devices and the listening port.

### Client side

For client side, we have to perform two actions: 1. Generate a proper DS-CUDA library supporting our connection protocol. 2. Compile our CUDA code using the DS-CUDA preprocessor and generate the executable.

For the first stage, we need to generate *libdscuda\_rpc.a* which is inside of the main path **\$dscudapath/src**. Then we need to compile our CUDA source code with the preproces-

30.00 +

20.00 =

50.00

WarnLevel: 2 searching DSCUDA servers.. recvfrom found server: "192.168.0.205" method of remote procedure call: TCP Socket automatic data recovery: off waiting for the server to be set up... Established a socket connection to 192.168.0.205:0 (port 65433) ... Client IP address : 192.168.0.205 try 0 /usr/local/DSCUDA/dscudapkg1.7.5.1/bin/ptx2symbol:25: warning: assigned but unused variable - args /usr/local/DSCUDA/dscudapkg1.7.5.1/bin/ptx2symbol:28: warning: assigned but unused variable - ts /usr/local/DSCUDA/dscudapkg1.7.5.1/lib/utility.rb:17: warning: assigned but unused variable - verbose\_default /usr/local/DSCUDA/dscudapkg1.7.5.1/lib/utility.rb:141: warning: assigned but unused variable - elsep /usr/local/DSCUDA/dscudapkg1.7.5.1/lib/utility.rb:142: warning: assigned but unused variable - ersep 39.00 + 6.00 = 45.00 51.00 = 41.00 +92.00 17.00 +63.00 = 80.00 10.00 + 44.00 = 54.00 41.00 + 13.00 =54.00 58.00 + 43.00 = 101.00 50.00 + 59.00 = 109.00 35.00 + 6.00 = 41.00 try 1 60.00 + 2.00 = 62.00 56.00 = 20.00 + 76.00 27.00 + 40.00 = 67.00 39.00 +13.00 =52.00 54.00 + 26.00 =80.00 46.00 + 35.00 = 81.00 51.00 +31.00 =82.00 26.00 = 9.00 +35.00 try 2 38.00 + 50.00 = 88.00 13.00 + 55.00 = 68.00 49.00 + 24.00 = 73.00 35.00 + 26.00 =61.00 37.00 +29.00 =66.00 23.00 = 5.00 + 28.00 41.00 = 24.00 + 65.00

Figure 4.5: Correct execution output from a DS-CUDA client.

sor *dscudacpp*, inside of the **\$dscudapath/bin** path. This will generate our executable which GPU code will run over the server side. Before the executable may be launched, we need to specify some DS-CUDA environment variables as well:DSCUDA\_WARNLEVEL = 2, DSCUDA\_REMOTECALL = tcp and DSCUDA\_SERVER = 192.168.0.205.

As we can observe in Figure 4.5, the GPU code is executed in one server machine addressed by the ip number 192.168.0.205, which is equipped with one GPU.

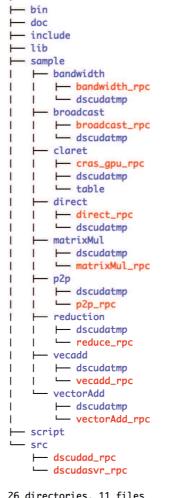

### 4.4 Development Contributions for DS-CUDA

In order to bring the power of GPGPU to mobile devices, specifically over Android platform, DS-CUDA was used as a medium to execute use remote GPU. We were able to adapt DS-CUDA framework to run in Android through 2 methods: 1. Using a terminal emulator and external ARM compiler. 2. Using NDK. As well, we develop a make file system based to maintain the SDK provided in DS-CUDA package. Also we provide a GitHub<sup>3</sup> support. Next sections we explain in detail these contributions.

<sup>&</sup>lt;sup>3</sup>Web based git repository hosting service.

Figure 4.6: System prototype to use DS-CUDA on Tablets.

### 4.4.1 Enabling Android Tablets

One of the motivations of this research was the idea of merging the world of mobility with high performance computing. In order to create new applications which the author depicted as the first idea when the whole process started, such as in Figures 1.1 & 1.2.

The purpose was connect the interactiveness and mobility capabilities of the tablet with applications that require exhaustive computation. A example system is shown in Figure 4.6. One tablet device connected to a local network through Wi-Fi and a DS-CUDA server equipped with one CUDA capable GPU interconnected to the same local network via Ethernet cable.

### Through terminal emulator

The first approach was using the terminal emulator. Inside of the huge Android app ecosystem, there is a terminal emulator shell or bash like. Inside of this emulator you can execute common Linux commands such as *ifconfig*, ./ and *cd* etc. Then, the basic idea was to compile a basic example from DS-CUDA sample package using an external ARM compiler. Copy the binary to the device and execute in terminal as a normal Linux based program. The full steps are detailed next:

### First

The scenario is depicted in figure 4.7. The *sample.cu* file contain the proper CUDA code to add some numbers. This file is inserted to dscudaccp preprocessor. The output is composed by several files: The *sample.ptx* correspond to low level like code inside of

Figure 4.7: Output of dscudacpp preprocessor.

Figure 4.8: Creation of client static library for ARM architecture.

the kernel wrriten in sample.cu. This is generated by nvcc compiler. The *samplerc.cpp* which is a similar version of the original code but wrapping all the native CUDA functions with the DS-CUDA proper ones. Last, the sample binary which is the final executable for desktop machines.

### Second

In order to be able to use the APIs from DS-CUDA on client side on the tablet, we need to generate *libdscuda\_rpc.a.* This library includes all the wrapper functions to communicate with the server and execute the CUDA code. We used an ARM compiler provided by ARM GNU/Linux tool chain to generate object files and then collapse these into the static library, as Figure 4.8

Figure 4.9: Creation DS-CUDA executable for ARM architecture.

Figure 4.10: Copy DS-CUDA executable to tablet.

### Third

The samplerc.cpp code is compiled with the ARM compiler and it is integrated with *libdscuda\_rcp.a* to create a final executable, Figure 4.9.

### Fourth

Finally, two files are copied manually (Via SD card or USB) into the tablet, Figure 4.10. We access this path under the terminal emulator and execute the binary.

The executable will send a copy of the .ptx to the server, which includes the CUDA code for the GPU. A final output from the tablet is pictured in Figure 4.11.

DS-CUDA was enabled by this method, and also the first trials of CUDA over Tablet devices. However, there are some week points about it: Due to usage of terminal emulator, displaying data is restricted only to text. If we require to implement an OpenGL app another way should be found. The process for compiling and testing is complicated, thus become impractically to develop. Copying and pasting the executable and .pxt code generate may damage the SD card and USB bay due to connect and disconnect action. At this point, DS-CUDA version 1.3.2 was using the Remote Procedure Call (RPC) library to interconnect the

Figure 4.11: DS-CUDA executed on Android terminal emulator.

Figure 4.12: Constitution of DS-CUDA client library version 1.3.2. RPC based.

client and server over Ethernet protocol using sockets. With this method, none modifications were made to compile libdscuda.a library. Nevertheless, NDK tool-kit is not capable of using such libraries.

### 4.4.2 Using Native Development Kit for Android

As we saw in the section above, running DS-CUDA using the terminal emulator allow us to use RPC libraries but limiting to develop shell console based application. One alternative to solve this issue is using NDK which was detailed in 3. The Native Development kit allow to use C code inside of the Java main based program on Android devices. The first trial was to compile the *libdscuda\_rpc.a* static library within NDK, however as the contents inside of the package shows, there is no support for RPC libraries inside of NDK. The client library for DS-CUDA version 1.3.2 uses RPC to implement the wrapper functions corresponding to the native CUDA API. A diagram of the contest are shown in Figure 4.12. The *dscudarpc.x* prototypes all the wrapper functions on RPC language, then using *rpcgen* generate the proper stubs for client, server, external data representation and headers in C language. The problem to compile these files corresponding to RPC, such as *dscudarpc\_clnt.c* is that NDK do not has some prototype values.

A new version of DS-CUDA is proposed, in which POSIX sockets were used instead of RPC library. The POSIX socket API is a viable inside of NDK enabling the communication with the external apps directly without calling into the Java layer. A socket is a connection end-point that can be named and addressed in order to transmit data between applications that are running either on the same machine or another machine on the network. Thus, the

Figure 4.13: Constitution of DS-CUDA client library version 1.5.2. TCP socket based.

new version of client library for DS-CUDA 1.5.2 is shown in Figure 4.13.

The *sockutil.c* file implements the set up connection between client and server, the received and sent message functions only using POSIX sockets. The prototype functions are shown bellow:

```

1 struct sockaddr_in setupSockaddr(unsigned int ipaddr, int ipport);

2 meid and MarBaccachet(int acchemente);

```

```

2 void sendMsgBySocket(int sock, char *msg);

```

```

3 void recvMsgBySocket(int sock, char *msg, int msgbufsize);

```

The source code named *libdscuda\_tcp.c* implements the remote call which carries the wrapper function to call native CUDA calls and send the proper data to the server side. Basically the implementation of the wrapper functions are the same, only the medium which are carried by is changed from RPC to TCP socket. The next step is to include the DS-CUDA client static library inside of the Java code. Initially, the first test included all the source code of the *libdscuda\_tcp.a* inside of the main project, lately we realized that every time we want to use DS-CUDA on the tablet we have to copy all the code. Then, we created a separated project in which only *libdscuda\_tcp.a* is generated. The sample of the Android.mk and Application.mk are showed next:

```

1 ## Android.mk

```

```

2 \frac{1}{1} \frac{

```

```

3 LOCAL_PATH := $(call my-dir)

```

```

4 include $(CLEAR_VARS)

```

```

5

```

```

6 LOCAL_MODULE := dscuda_tcp1.5.2

```

```

7

```

```

8 LOCAL_CFLAGS := -O0 - g - ffast - math - funroll - loops - I.

```

```

9 -I/usr/local/cuda/include \setminus

```

```

10 -I/usr/local/cuda-4.1/NVIDIA_GPU_Computing_SDK/C/common/inc

```

```

11 -I/usr/local/cuda/samples/common/inc -DTCP_ONLY=1

```

```

12 LOCAL_SRC_FILES := dscudaverb.cpp dscudautil.cpp \

```

```

13 sockutil.c libdscuda_tcp.cpp \setminus

```

14 LOCAL\_LDLIBS := -1d1 - 1log

```

15 include $(BUILD_STATIC_LIBRARY)

```

16 #####################Static Library DS-CUDA Routine

As we can observe, all the source code inside of Figure 4.13 is included inside of the Android.mk. Some flags are also included, such as debugging, fast mathematics and unroll. Some local libraries from the NDK are also called such as the log library.

```

1 ## Application.mk

```

- 2 APP\_MODULES :=  $dscuda_tcp1.5.2$

- 3 APP\_ABI := armeabi

- 4 APP\_PLATFORM := android 18

- 5 APP\_STL := gnustl\_static

6 APP\_GNUSTL\_FORCE\_CPP\_FEATURES := exceptions rtti

7 APP\_OPTIM := debug

The Application.mk file configures the platform, type of C library to load, architecture and some exceptions for the compiler to use at the time to generate the code. To include the *libdscuda\_tcp.a* in another project just use the *include* command inside of the Android.mk file, writing the full path where the static library is located. Include the project as *BUILD\_STATIC\_LIBRARY* inside just above the compilation line where the main preprocessed CUDA code is located. As a sample, we show a bandwidth sample program which measures the memory transfer between the tablet and the remote GPU. Figure 4.14 shows the output of this app.

The entire Android.mk code for the bandwidth app is showed below:

```

2 LIB_LOCAL_PATH := $(call my-dir)

```

```

3 include /usr/local/DSCUDA/dscudapkg1.5.2/src/Android/jni/Android.mk

```

```

4 LOCAL_PATH := (LIB_LOCAL_PATH)

```

```

6 include $(CLEAR_VARS)

```

```

7

```

```

8 LOCALMODULE := bandwidth

```

```

9

```

```

10 LOCAL_CFLAGS := -O0 - g - P - ffast - math - funroll - loops - fpermissive - I. \setminus

```

11  $-I/usr/local/cuda/include \setminus$

```

12 -I/usr/local/DSCUDA/dscudapkg1.5.2/include/common/inc

```

```

13 -I/usr/local/cuda/samples/common/inc -DTCP_ONLY=1

```

14

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>V</b> 9:44 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Bandwidth BandwithDSCUDA                                                                                                                                                                                                                                                                                                                                                                                                                                       | :             |

| DS-CUDA Bandwidth Test                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

| Starting Bandwidth Test H2D<br>Info:<br>Max size:1048576 Byte<br>PKGsize:1024 Byte<br>LOOP:200000                                                                                                                                                                                                                                                                                                                                                              |               |

| # 1 device found.                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| #<br># cudaMemcpy (HostToDevice)<br>#<br>1024 byte 0.841228 sec 0.237748 MB/s<br>2048 byte 0.700406 sec 0.285549 MB/s<br>4096 byte 0.360058 sec 0.555466 MB/s<br>8192 byte 0.222334 sec 0.899548 MB/s<br>16384 byte 0.097184 sec 2.057953 MB/s<br>32768 byte 0.082456 sec 2.425533 MB/s<br>65536 byte 0.172687 sec 1.158166 MB/s<br>131072 byte 0.059210 sec 3.377804 MB/s<br>262144 byte 0.037361 sec 5.353155 MB/s<br>524288 byte 0.057462 sec 3.480562 MB/s |               |

| MemHost2Dev                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MemDev2Host   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

Figure 4.14: Bandwidth sample output. Tablet performing memory transfer to the remote GPU using DS-CUDA.

```

LOCAL\_SRC\_FILES := bandwidth.cpp

15

16

LOCAL_STATIC_LIBRARIES := dscuda_tcp1.5.2

17

LOCAL\_LDLIBS := -1d1 - 1log

18

include $(BUILD_STATIC_LIBRARY)

19

20

include $(CLEAR_VARS)

21

22

LOCALMODULE := bandwidthtest

23

24

LOCAL\_CFLAGS := -g -W - DANDROID\_NDK - DDISABLE\_IMPORTGL

25

LOCAL\_SRC\_FILES := app-android.cpp

26

27

LOCAL_STATIC_LIBRARIES := bandwidth

LOCAL\_LDLIBS := -1d1 - 1log

28

29

include $(BUILD_SHARED_LIBRARY)

30

```

### 4.4.3 Makefile script for DS-CUDA SDK